In a step toward computers that mimic the parallel processing of complex biological brains, researchers from HRL Laboratories, LLC, and the University of Michigan have built a type of artificial synapse.

They have demonstrated the first functioning “memristor” array stacked on a conventional complementary metal-oxide semiconductor (CMOS) circuit. Memristors combine the functions of memory and logic, like the synapses of biological brains.

The work is part of the Defense Advanced Research Projects Agency’s (DARPA) SyNAPSE Program, or Systems of Neuromorphic Adaptive Plastic Scalable Electronics. Since 2008, the HRL-led SyNAPSE team has been developing a new paradigm for “neuromorphic computing” modeled after biology.

In a conventional computer, logic and memory functions are located in different parts of the circuit and each computing unit is only connected to a handful of neighboring units. While conventional digital computing has the speed and complexity to emulate lower hierarchy animal intelligence, it is still far from matching the efficiency, density and associated energy dissipation of complex biological brains.

In contrast, a brain has neurons connected to each other by synapses, which act as reconfigurable switches that can form pathways linking thousands of neurons. This enables a brain to perform many operations simultaneously, or in parallel. A human, for example, can recognize a face in an instant exceeding the speed of even a supercomputer.

R-RAM

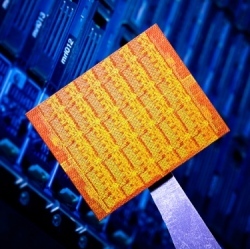

The researchers developed a vertically integrated hybrid electronic circuit by combining the novel memristor developed at the University of Michigan with wafer scale heterogeneous process integration methodology and CMOS read/write circuitry developed at HRL. “This hybrid circuit is a critical advance in developing intelligent machines,” said HRL SyNAPSE program manager and principal investigator Narayan Srinivasa. “We have created a multi-bit fully addressable memory storage capability with a density of up to 30 Gbits/cm2, which is unprecedented in microelectronics.”

Industry is seeking hybrid systems such as this one, the researchers say. Dubbed “R-RAM,” they could shatter the looming limits of Moore’s Law, which predicts a doubling of transistor density and therefore chip speed every two years.

“We’re reaching the fundamental limits of transistor scaling. This hybrid integration opens many opportunities for greater memory capacity and higher performance of conventional computers. It has great potential in future non-volatile memory that would improve upon today’s Flash, as well as reconfigurable circuits,” said Wei Lu, an associate professor at the U-M Department of Electrical Engineering and Computer Science, whose group developed the memristor array.

Ultimately, the team plans to scale the neuromorphic chip to support millions of (simulated) neurons and billions of (simulated) synapses, thereby enabling the development of intelligent machines that can learn from their environments and exhibit complex behaviors. The technology has numerous real-world applications in complex computing, including visual perception, planning, decision making, and navigation.